# University of California, Santa Barbara

Department of Electrical and Computer Engineering

ECE 152A - Digital Design Principles

Midterm Exam #2 – Solution August 5, 2009

| Name                   |  |

|------------------------|--|

| Perm #                 |  |

| Lab Section            |  |

|                        |  |

| Problem #1 (35 points) |  |

| Problem #2 (35 points) |  |

| Problem #3 (30 points) |  |

| Total (100 points)     |  |

- This is a 75 minute exam; closed book, closed notes, no calculators.

- Answer all questions on the exam.

## Problem #1.

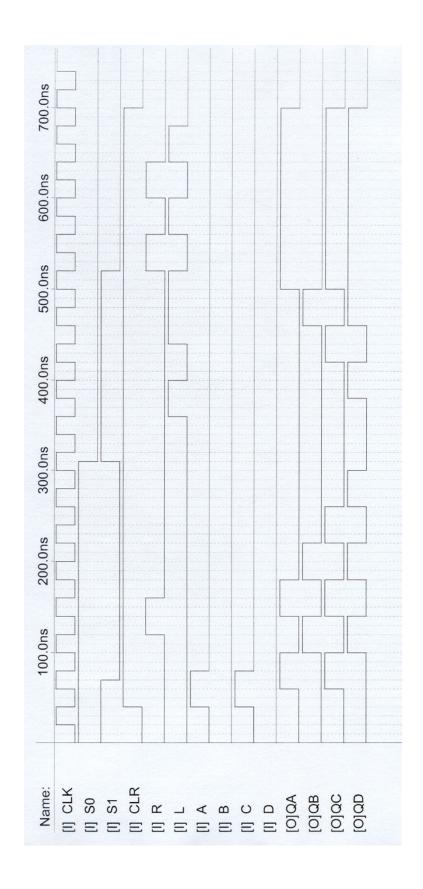

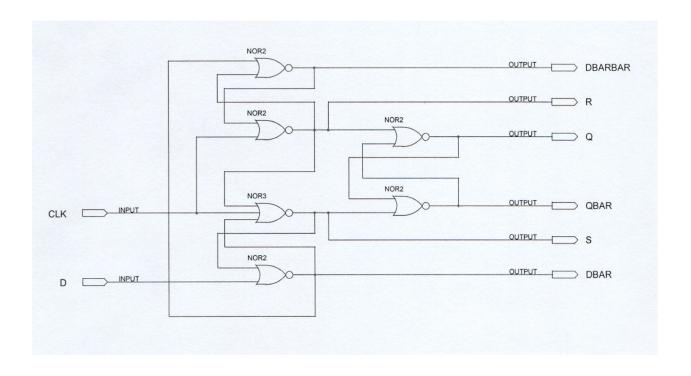

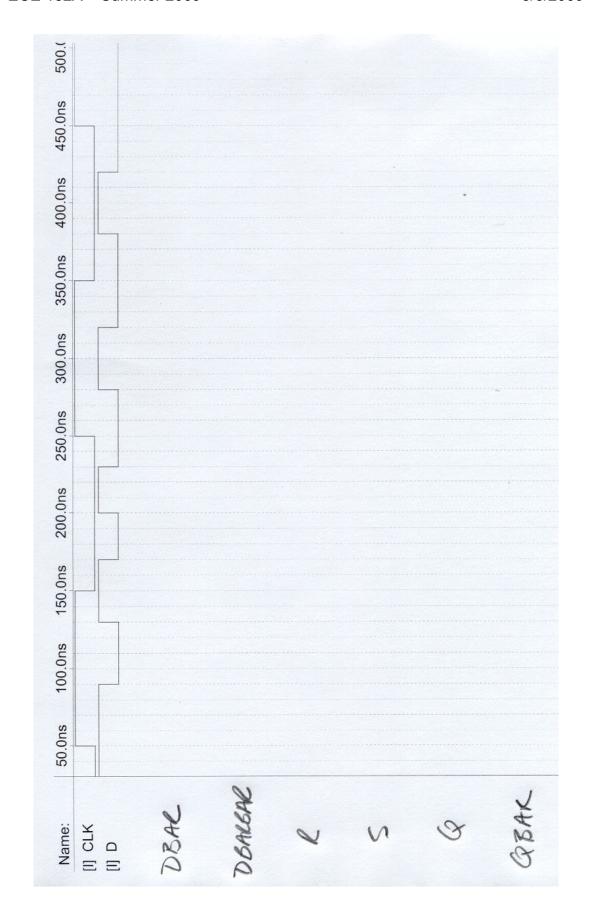

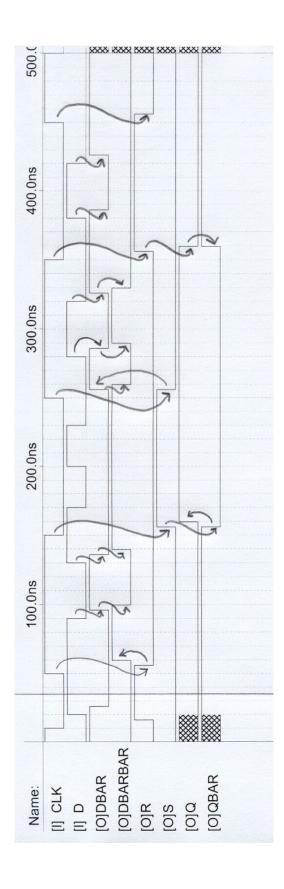

a) (26 points) For the edge-triggered D Flip-Flop shown below, complete the timing diagram on the following page. The actual propagation delays are not important, but use arrows to indicate the causality and order of transitions.

Assume the following initial conditions:

Midterm Exam #2 Solution - Page 3 of 18

b) (3 points) Assuming that  $t_{PHL} = t_{PLH} = 10$ ns for both the 2 and 3 input NOR gates, what is the worst case CLK to Q propagation delay?

c) (3 points) If fundamental mode operation is assumed (and guaranteed) and the propagation delays are as specified in part b) above, what is the set up time for this flip flop?

d) (3 points) If this flip flop is used in a digital system in conjunction with a combinational logic block having a critical path delay of 50ns, what is the minimum clock period for this system?

## Problem #2.

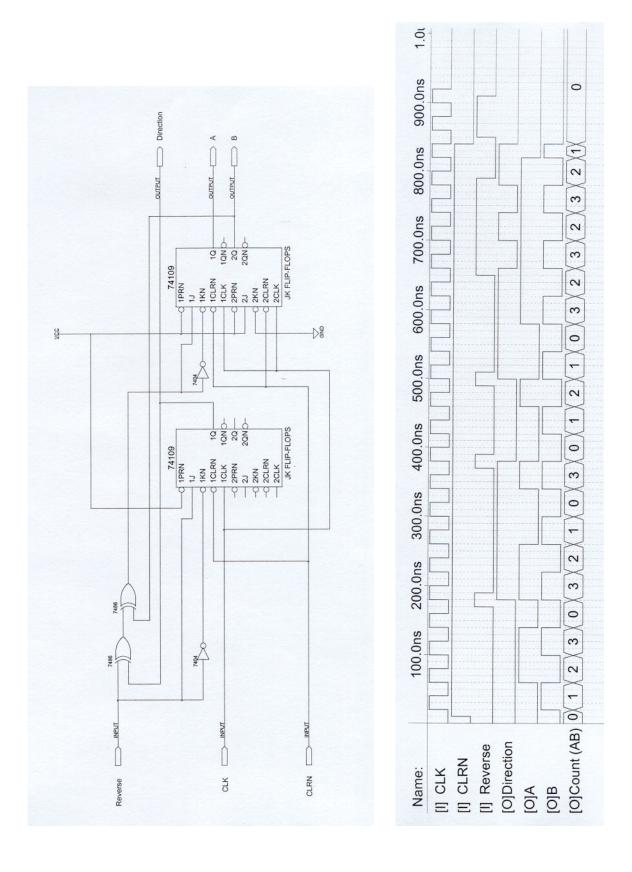

In this problem you are asked to design a 2-bit up/down binary counter. The counter has a single input R (Reverse). When R is 0, the counter continues counting in the current direction (up or down) on each clock edge. When R is 1, the direction is reversed i.e., if the counter had been counting up, it now counts down, if the counter had been counting down, it now begins counting up. Note that R doesn't *specify* the direction, it *reverses* the current direction.

The design may require more than two state variables, but the count <u>must</u> be represented by the two least significant state variables which <u>must</u> be labeled A and B (where B is the least significant bit).

When counting up: AB =  $00 \rightarrow 01 \rightarrow 10 \rightarrow 11 \rightarrow 00...$ When counting down: AB =  $11 \rightarrow 10 \rightarrow 01 \rightarrow 00 \rightarrow 11...$

The count should change on every clock edge whether reversing direction or not.

a) (5 points) Construct a state diagram for your design. Clearly indicate the definition of each state variable in your design.

b) (10 points) Construct a state table for your design.

| R         | D   | A | 6      | D    | A   | B    |

|-----------|-----|---|--------|------|-----|------|

| 0000 0000 | 0   | 0 | 0      | 0    | 0   | 1    |

| 0         | 0   | 0 | 1      | 0000 | 1   | 010  |

| 0         | 0   | 1 | 0      | 0    | 1   | 1    |

| 0         | 0   | 1 | 1      | 0    | 0   | 0    |

| 4         |     |   |        | 1    | 100 |      |

| 0         | 1   | 0 | 0      | 1    | 1   | 1    |

| 0         | 1   | 0 | 1      | 1    | 0   | 0    |

| 0         | 1   | 1 | 0      | 1    | 0   | 1    |

| 0         | 1   | 1 | 1      | 1-   | 1   | 0    |

|           |     |   | 010101 |      |     | 1010 |

| 1         | 0   | 0 | 0      | 1    | 1   | 1    |

| 1         | 0   | 0 | 1      | 1    | 0   | 0    |

| 1         | 000 | 1 | 0      | 1    | 0   | 0    |

| 1         | 0   | 1 | 1      | 1    | 1   | 0    |

|           |     |   |        |      | 001 |      |

| 1         | 1   | 0 | 0      | 0    | 0   | 1    |

| 1         | 1   | 0 | 1      | 0    | 1   | 0    |

| 1         | 1   | 1 | 0      | 0    | 1   | 1    |

| 1         | 1   | 1 | 1      | 0    | 0   | 0    |

|           |     |   |        |      |     |      |

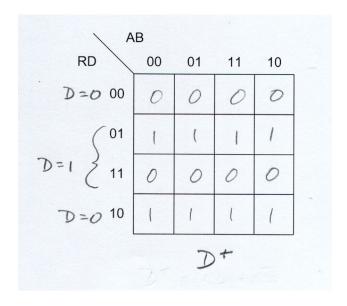

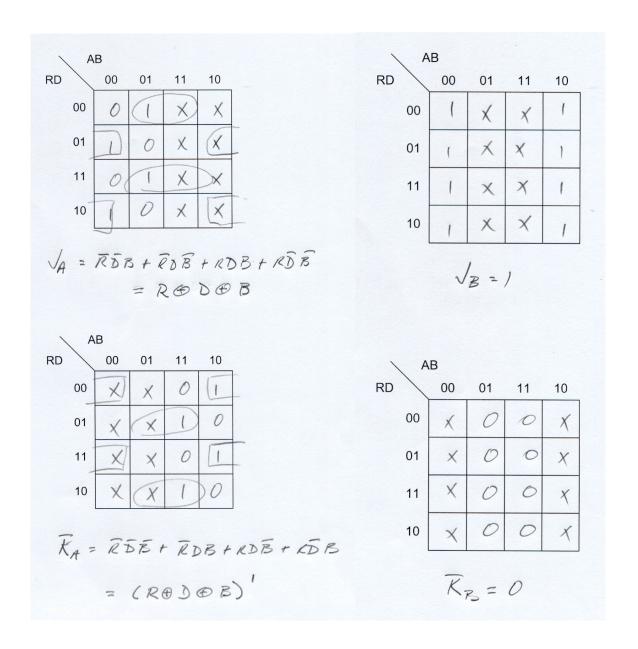

c) (5 points) Construct next state maps for each of the state variables in your design.

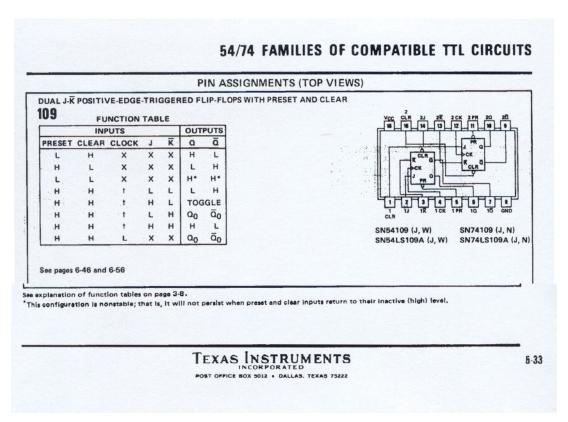

d) (5 points) Marketing has determined that if 74109 "J – not K" flip flops are used, profit margins will be maximized. The pin assignments and function table for the device are given below.

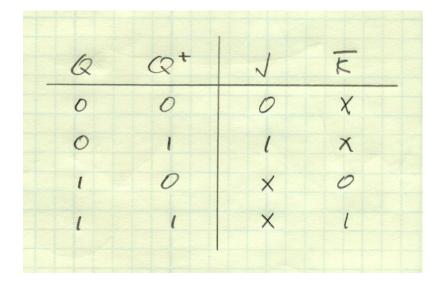

Construct the excitation table for the "J – not K" flip flop.

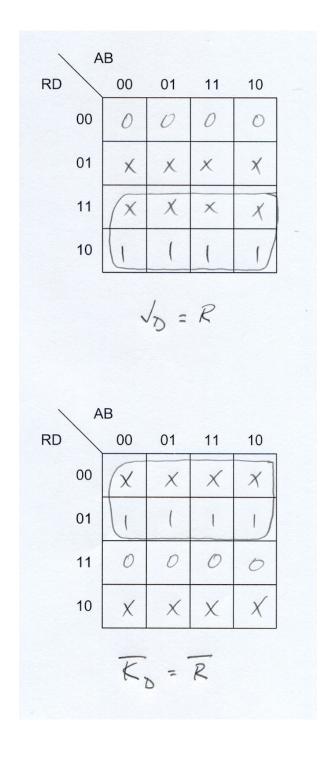

e) (10 points) Based on the excitation table derived in part d) above, determine the flip flop inputs for each of the state variables. You can assume that the preset and clear inputs are always tied to a logical 1.

## Problem #3.

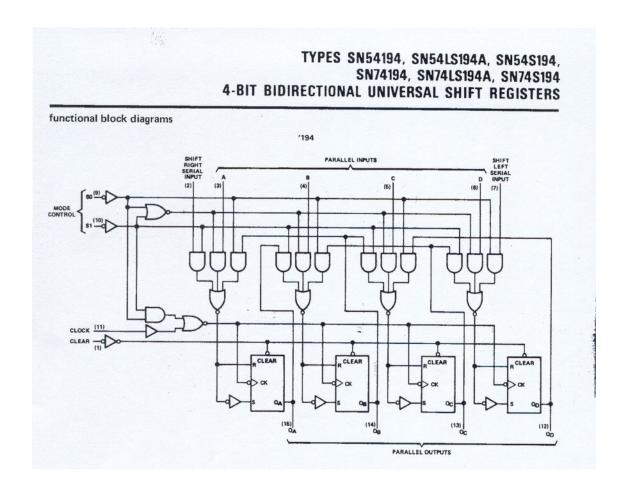

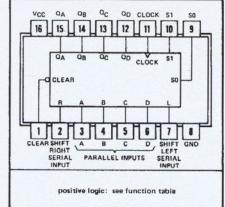

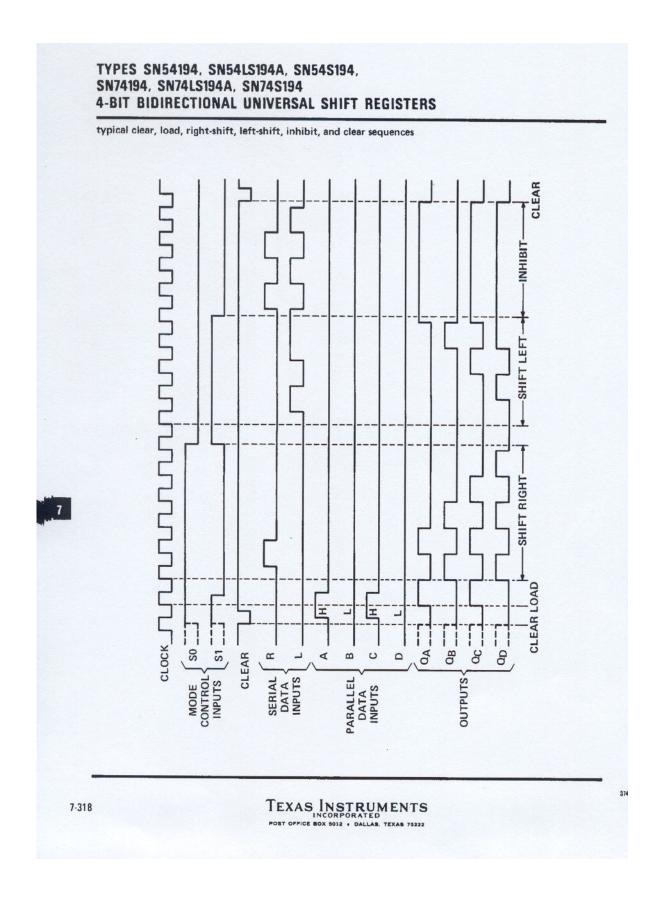

On this and the following two pages are the functional block diagram, data sheet and timing diagram, respectively, for the SN74194 4-Bit Bidirectional Universal Shift Register.

The Function Table on the data sheet on the following page provides all the information necessary to complete this design, but I've included all three pages from "The TTL Data Book for Design Engineers" so that there will be no ambiguity as to how this device operates.

On the final pages of this exam, give the Verilog code that, when synthesized, will implement the SN74194 on an FPGA. Use the signal names given in the module declaration in your design.

The syntax of your design will be checked very carefully to determine if it meets the specification.

TTL MSI

#### TYPES SN54194, SN54LS194A, SN54S194, SN74194, SN74LS194A, SN74S194 4-BIT BIDIRECTIONAL UNIVERSAL SHIFT REGISTERS BULLETIN NO. DL-S 7611866, MARCH 1974-REVISED OCTOBER 1976

- Parallel Inputs and Outputs

- Four Operating Modes: Synchronous Parallel Load Right Shift Left Shift Do Nothing

- Positive Edge-Triggered Clocking

- **Direct Overriding Clear**

| TYPE    | TYPICAL<br>MAXIMUM<br>CLOCK<br>FREQUENCY | TYPICAL<br>POWER<br>DISSIPATIO |  |  |  |

|---------|------------------------------------------|--------------------------------|--|--|--|

| '194    | 36 MHz                                   | 195 mW                         |  |  |  |

| 'LS194A | 36 MHz                                   | 75 mW                          |  |  |  |

| 'S194   | 105 MHz                                  | 425 mW                         |  |  |  |

SN54194, SN54LS194A, SN54S194 . . . J OR W PACKAGE SN74194, SN74LS194A, SN74S194 . . . J OR N PACKAGE (TOP VIEW) Q<sub>C</sub> QD CLOCK S1 16 15 14 13 12 11 10 9

#### description

These bidirectional shift registers are designed to incorporate virtually all of the features a system designer may want in a shift register. The circuit contains 46 equivalent gates and features parallel inputs, parallel outputs, right-shift and left-shift serial inputs, operating-mode-control inputs, and a direct overriding clear line. The register has four distinct modes of operation, namely:

> Parallel (broadside) load Shift right (in the direction QA toward QD) Shift left (in the direction QD toward QA) Inhibit clock (do nothing)

Synchronous parallel loading is accomplished by applying the four bits of data and taking both mode control inputs, S0 and S1, high. The data are loaded into the associated flip-flops and appear at the outputs after the positive transistion of the clock input. During loading, serial data flow is inhibited.

Shift right is accomplished synchronously with the rising edge of the clock pulse when S0 is high and S1 is low. Serial data for this mode is entered at the shift-right data input. When SO is low and S1 is high, data shifts left synchronously and new data is entered at the shift-left serial input.

Clocking of the flip-flop is inhibited when both mode control inputs are low. The mode controls of the SN54194/SN74194 should be changed only while the clock input is high.

**FUNCTION TABLE**

| INPUTS |      |    |       |        |       |          | OUTPUTS |   |   |     |     |                 |                |

|--------|------|----|-------|--------|-------|----------|---------|---|---|-----|-----|-----------------|----------------|

| CLEAR  | MODE |    | CLOCK | SERIAL |       | PARALLEL |         |   |   |     | _   |                 |                |

|        | S1   | SO | CLOCK | LEFT   | RIGHT | A        | В       | С | D | QA  | αB  | ac              | Q <sub>D</sub> |

| L      | X    | X  | X     | X      | X     | X        | X       | X | × | L   | L   | L               | L              |

| Н      | X    | X  | L     | ×      | · X   | X        | X       | X | X | QAO | QBO | aco             | QDO            |

| н      | Н    | н  | t-    | X      | ×     | a        | b       | c | d | a   | b   | C               | d              |

| н      | L    | н  | t     | ×      | н     | X        | X       | X | × | Н   | QAn | QBn             | QCn            |

| Н      | L.   | Н. | 1.    | X      | L     | ×        | X       | X | X | L   | QAn |                 | QCn            |

| Н      | Н    | L  | 1     | н      | X     | ×        | X       | X | X |     | QCn |                 | н              |

| н      | H    | L  | t     | L      | X     | x        | X       | X | X | QBn | QCn | QDn             | L              |

| н      | L    | L  | . X   | ×      | X     | X        | X       | X | X | QAO | QBO | Q <sub>C0</sub> | apo            |

- H = high level (steady state) L = low level (steady state)

- X = irrelevant (any input, including transitions)

- ↑ = transition from low to high level

- a, b, c, d = the level of steady-state input at inputs A, B, C, or D, respectively.

- QAO, QBO, QCO, QDO = the level of QA, QB, QC, or QD, respectively, before the indicated steady-state input conditions were established.

- Q<sub>An</sub>, Q<sub>Bn</sub>, Q<sub>Cn</sub>, Q<sub>Dn</sub> = the level of Q<sub>A</sub>, Q<sub>B</sub>, Q<sub>C</sub>, respectively, before the most-recent ↑ transition of the clock.

1076

7-316

TEXAS INSTRUMENTS OFFICE BOX 5012 . DALLAS, TEXAS 75222

```

// module SN74194 (QA, QB, QC, QD, CLR, S1, S0, CLK, L, R, A, B, C, D);

// (6 points for structure and "always" syntax; 6 points per operation)

module SN74194 (QA, QB, QC, QD, CLR, S1, S0, CLK, L, R, A, B, C, D);

output QA, QB, QC, QD;

input CLR, S1, S0, CLK, L, R, A, B, C, D;

reg QA, QB, QC, QD;

always @ (posedge CLK or negedge CLR) // this must be negedge CLR,

// not just CLR...

if (!CLR)

// CLR is the highest priority, so it must

begin

// be tested first...it overrides the values

OA <= 0;

// of S1 and S0

QB \leq 0;

QC <= 0;

OD <= 0;

end

else if (S1 && S0)

begin

// S1 == S0 == 1

QA \ll A;

// is the parallel load

QB \le B;

QC <= C;

// operation

QD \ll D;

end

else if (!S1 && S0) // shift right (toward QD)

begin

QA \ll R;

QB <= QA; // if blocking assignments are used QC <= QB; // the order must be reversed, other

// the order must be reversed, otherwise

// R would be loaded into all registers

QD \leftarrow QC;

else if (S1 && !S0) // shift left (toward QA)

begin

QA <= QB; // this order would actually

// work for either blocking

QB <= QC;

QC <= QD;

// of non-blocking assignments

QD \leftarrow L;

end

// you could include a test for S1 == S0 == 0

// or a default else, but since the action is

// to do nothing, it's not necessary

```

// endmodule

endmodule